The New Deep Learning Memory Architectures You Should Know About — eSilicon Technical Article | ChipEstimate.com

Arch-Net: A Family Of Neural Networks Built With Operators To Bridge The Gap Between Computer Architecture of ASIC Chips And Neural Network Model Architectures - MarkTechPost

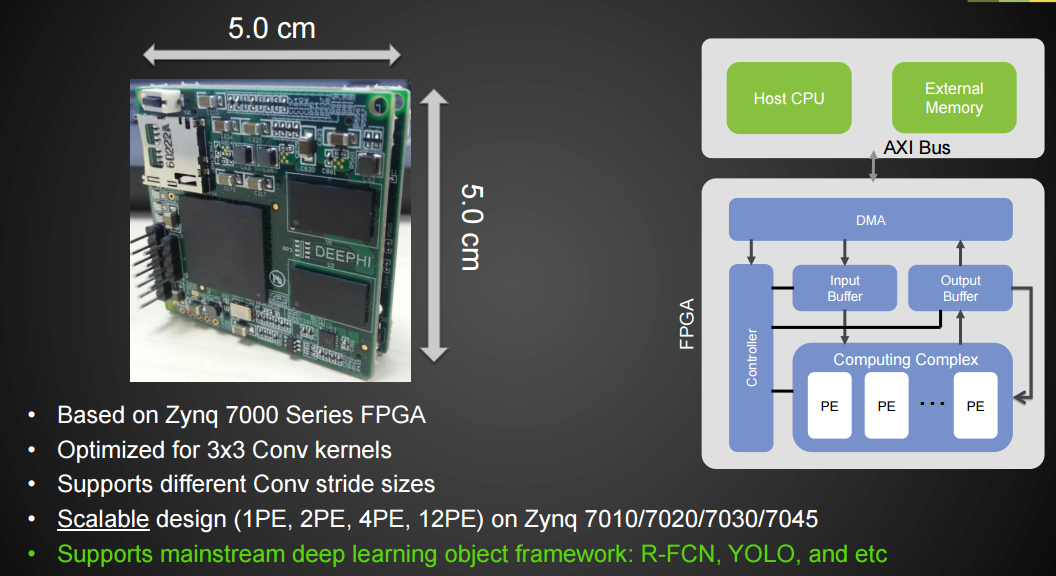

Blog: Aldec Blog - How to develop high-performance deep neural network object detection/recognition applications for FPGA-based edge devices - FirstEDA

Gartner - What trends will dominate this year's #AI landscape? Take a look at Gartner's Hype Cycle for AI, 2021 to find out: https://gtnr.it/3nY2QbC #GartnerSYM | Facebook

Buy Deep Neural Network ASICs The Ultimate Step-By-Step Guide Book Online at Low Prices in India | Deep Neural Network ASICs The Ultimate Step-By-Step Guide Reviews & Ratings - Amazon.in

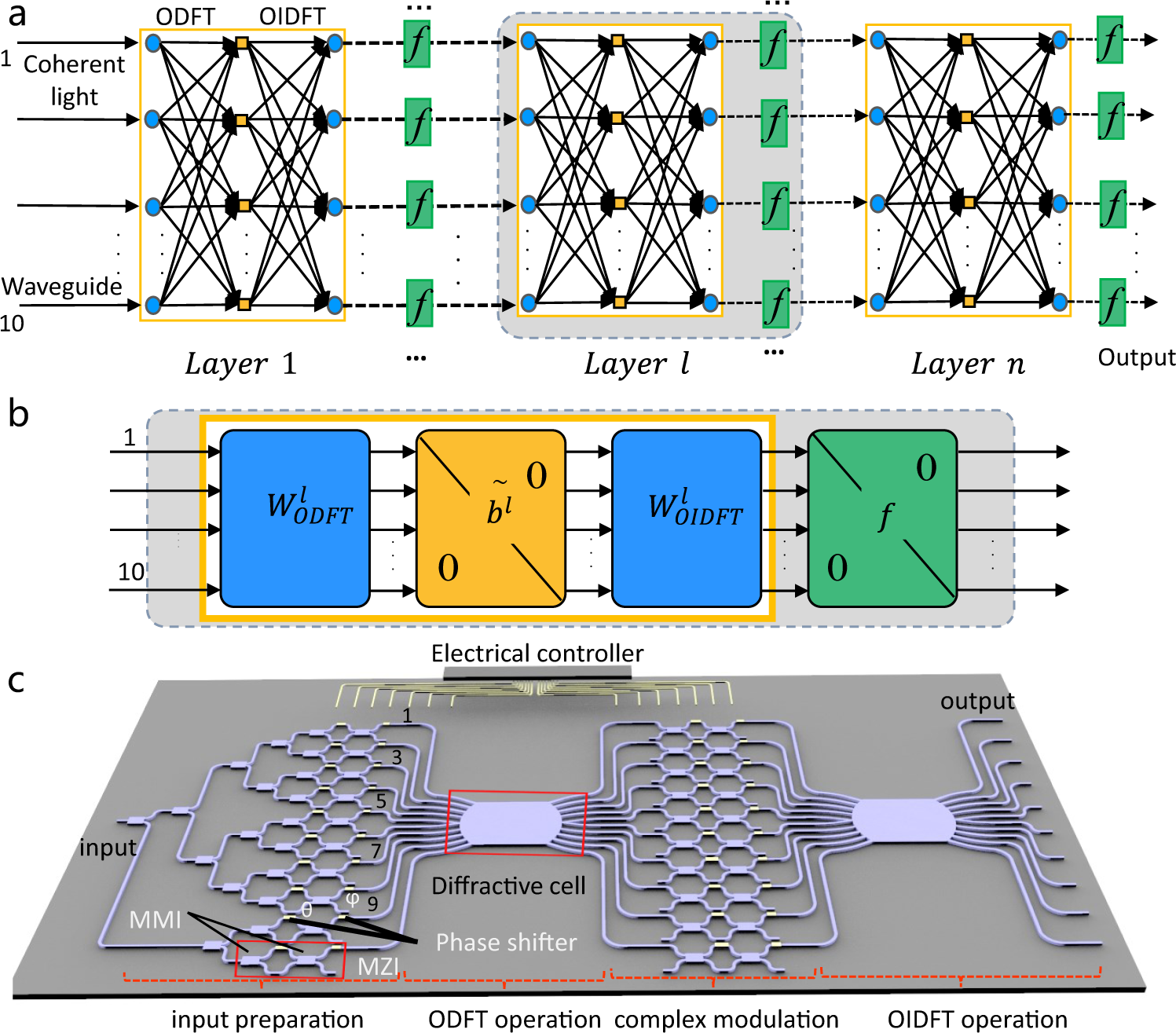

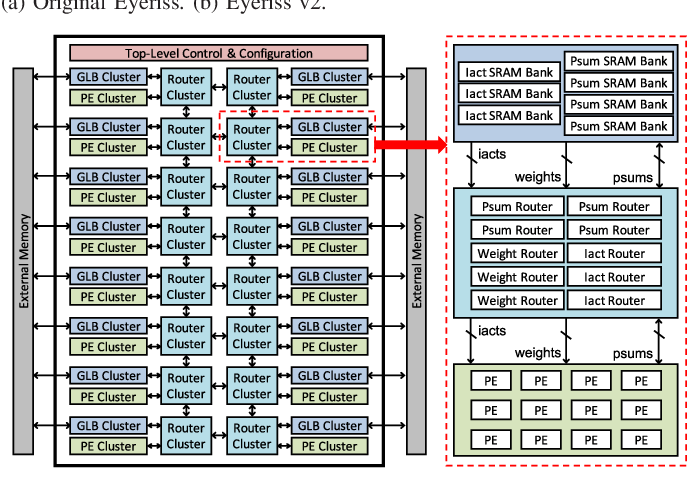

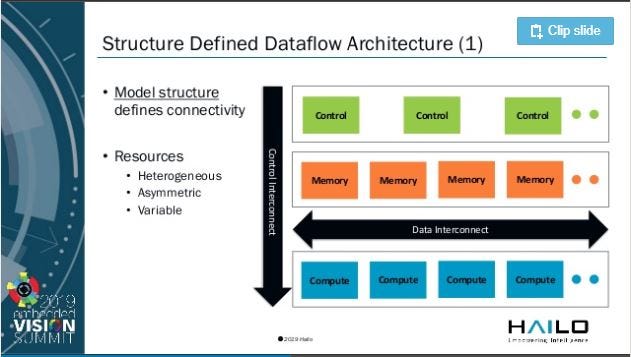

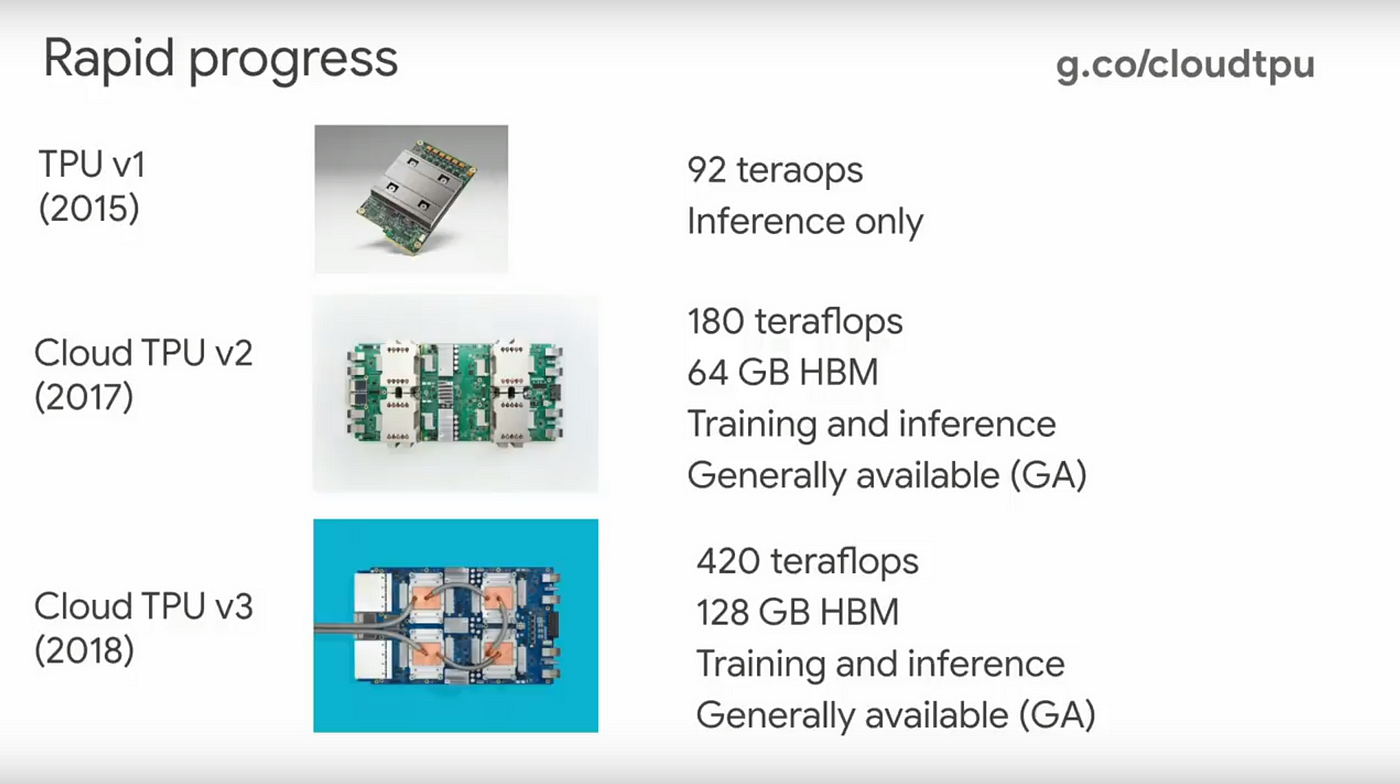

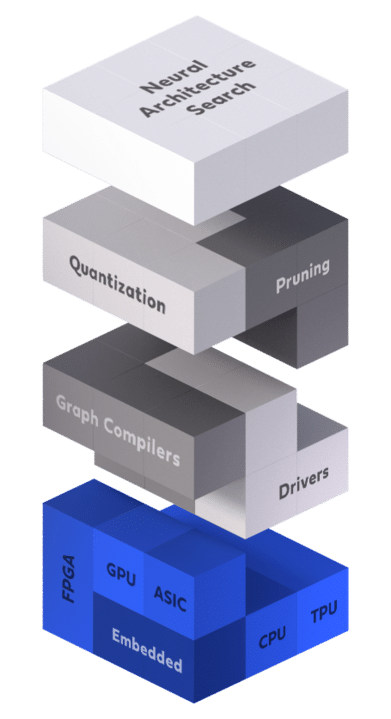

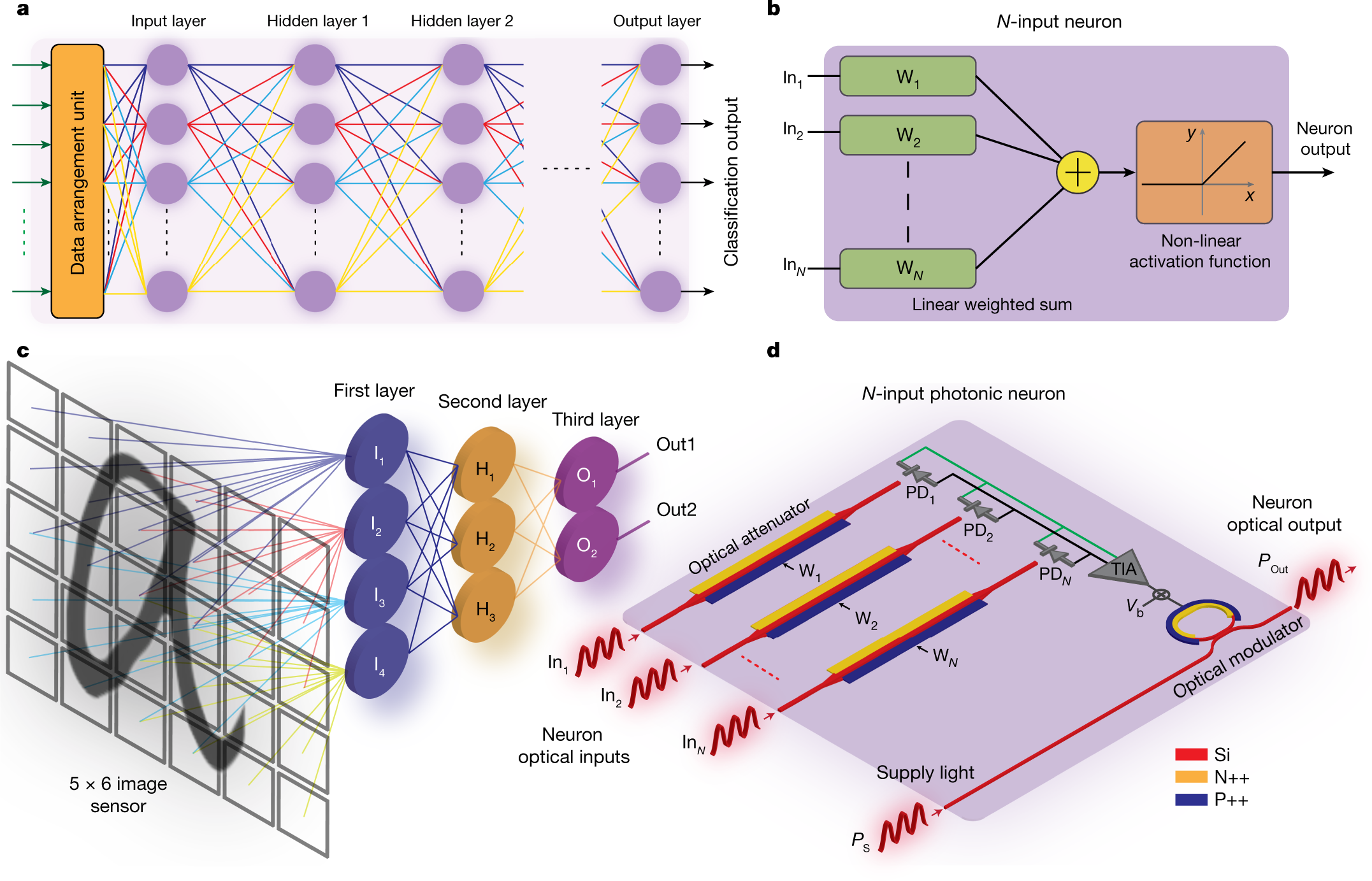

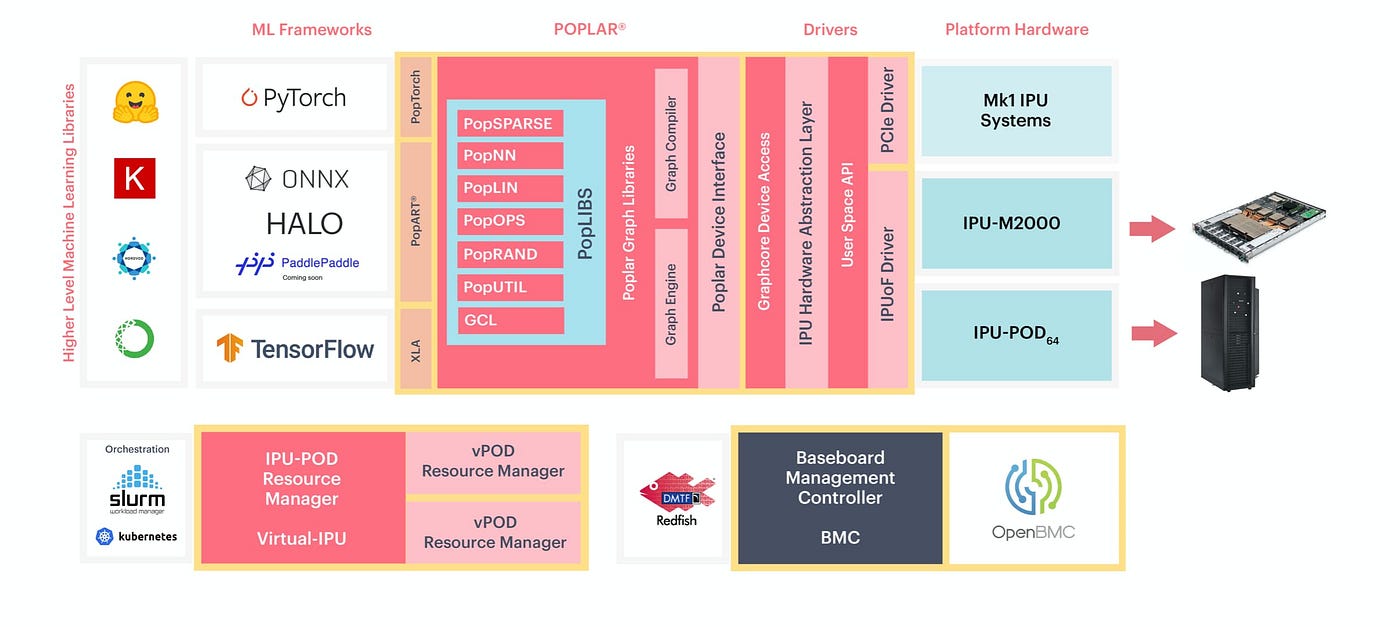

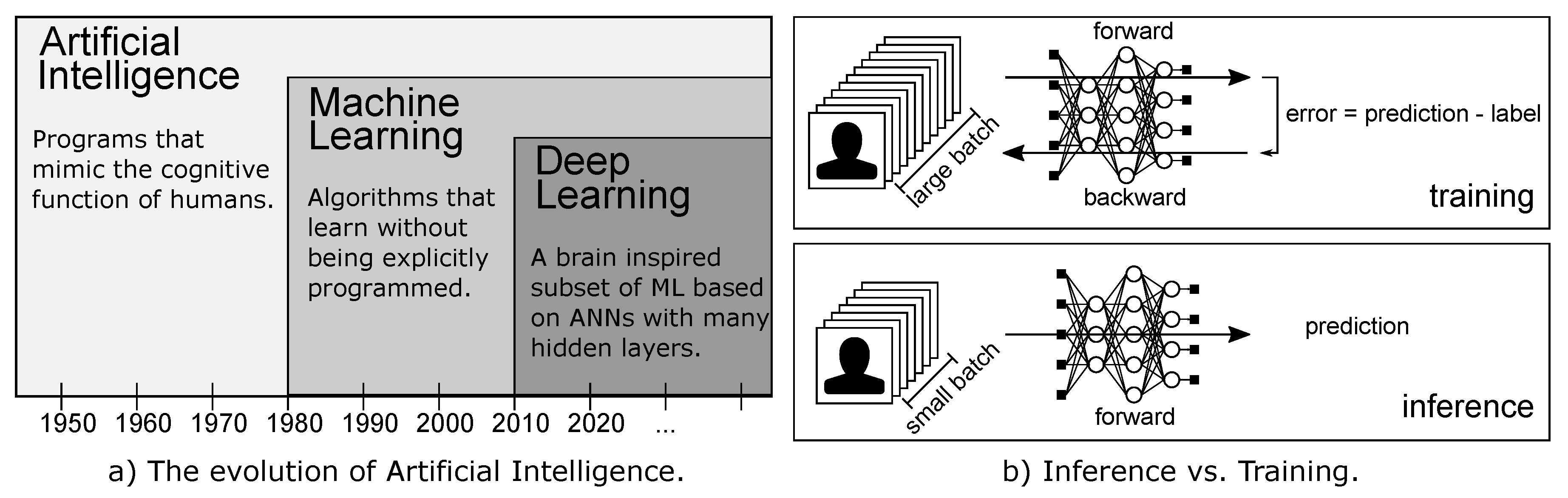

Future Internet | Free Full-Text | An Updated Survey of Efficient Hardware Architectures for Accelerating Deep Convolutional Neural Networks

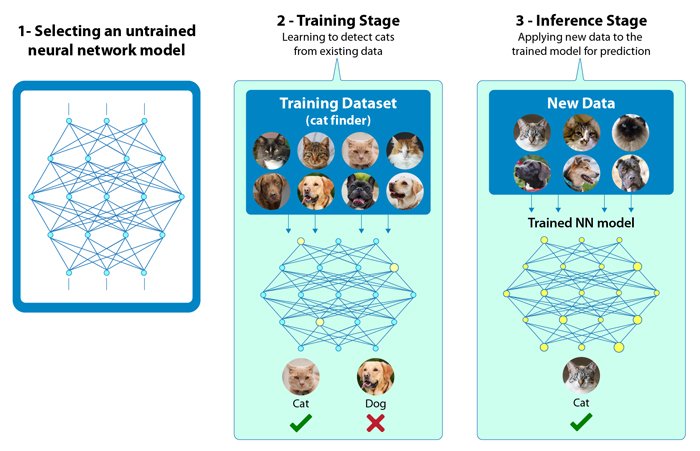

How to Develop High-Performance Deep Neural Network Object Detection/Recognition Applications for FPGA-based Edge Devices - Embedded Computing Design